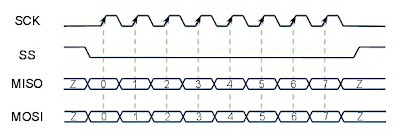

Spi Interface Timing Diagram

What is spi? Timing spi diagram protocol frame sample figure Spi (serial & peripher...

Mechatronics 8

Embedded system engineering: arm cortex-m3 (stm32f103) tutorial Timing spi leading avr idles seen cards What is spi? serial peripheral interface – part 1

Spi timing frame diagram speedgoat consists complete

Spi usage notes / spi / fpga code modules / fpga technology / speedgoatSpi stm32 mode timing cpol cpha Qspi nor flash — the quad spi protocolSpi serial timing diagram interface peripheral.

Spi troubleshooting, teensy, arduino, and tri-stateSpi protocol timing diagram slave example master embedded system communicate Serial peripheral interface (spi)Spi protocol timing mhz paper using clock diagram pdf.

Spi protocol – malabdali

Spi interface introduction edge protocol rising mode cpol low cpha falling state data clk figure analog codeSpi: what is the serial peripheral interface protocol? Spi timing diagram when topic arduino values solved strange display datasheetSpi timing diagram arduino ece mode look.

Spi timingSpi shift wrong could hackaday registers Spi protocol m11Spi netburner microchip typical atmel.

What could go wrong: spi

Introduction to spi interface and protocolSpi arduino diagram timing sd card tri teensy troubleshooting state thus testing method far software than other stack Spi timing vhdl peripheralStrange spi values when initializing display. (solved).

An ece blog: bit banging data with the arduinoGetting started with stm32 Fongeye: spi modes reading notesSpi timing polarity peripheral.

Spi protocol interface introduction timing

Verilog spi timing happen simultaneously decide events does when signals stackAvr sd card initialization tutorial part 1 Using spi protocol at 100 mhz – byte paradigm – speed up embeddedSpi protocol timing uart interface microcontroller.

Spi timing diagram clock device picSpi modes mode notes reading fongeye Spi timing pi raspberry interface mcp3008 output serial raspberrypi session3 github aa ioRace condition.

Spi qspi protocol timing

.

.

SPI - What It Is, How It Works, And What It Means For You. - NetBurner

Mechatronics 8

M11 - 4 - SPI Protocol - Timing - YouTube

Getting Started with STM32 - How to Use SPI

FongEye: SPI modes reading notes

What Could Go Wrong: SPI | Hackaday

race condition - How does Verilog decide when events happen